# A 1-Watt Flyback Converter Using the Si9100

#### INTRODUCTION

The Si9100 is a monolithic BiC/DMOS SMARTPOWER IC which combines high-efficiency CMOS logic, a high-voltage switching transistor and high-voltage pre-regulator on a single die. It is the first low-cost, high efficiency regulator designed to operate directly from unregulated high-voltage dc power sources in areas such as telecommunications and avionics. The primary application will be in feature phones and ISDN terminals to power the logic components without exceeding the load limits set by the telecommunications industry. Power integrated circuit technology allows low-power CMOS control circuits to be combined with DMOS power transistors in the Si9100. The resulting reduced parts count decreases system cost, improves reliability, and simplifies circuit design.

The flyback converter presented here uses the Si9100 to provide an isolated  $\pm$ 5-V supply rated at 1 W. Specifications for this supply are as follows:

Input Voltage ........... 15 to 70 V<sub>DC</sub> Maximum load .....+5 V @ 167 mA, -5 V @ 33 mA Minimum load .....+5 V @ 32 mA,

Regulation  $\dots \pm 5\%$ Maximum Ripple ..... 100 mV p-p Switching Frequency . . . . . 100 kHz

Efficiency ...... 80% min for 1 W load

75% min for 0.2 W load

-5 V @ 8 mA

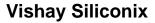

A schematic for the flyback converter is found in Figure 1, with a parts list provided in Appendix B. However, before discussing the details of the power supply design, it is instructive to review the functions of the Si9100 integrated circuit.

FIGURE 1. Schematic Diagram of the Si9100 Discontinuous Flyback Converter Circuit

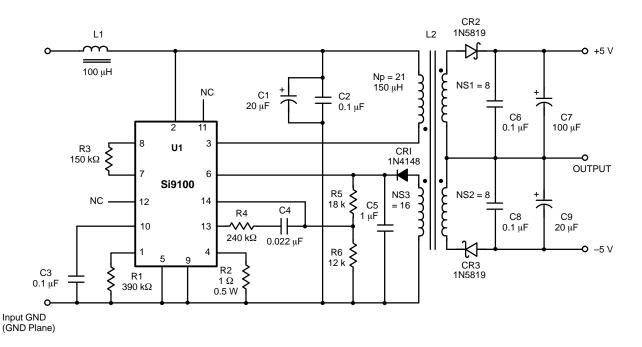

FIGURE 2. Si9100 Simplified Block Diagram

#### **SI9100 DESCRIPTION**

As shown in the block diagram of Figure 2, the Si9100 combines an oscillator, pre-regulator/start-up circuit, precision voltage reference, error amplifier, current-mode controller, and a MOSFET switching transistor into one 14-pin dual-in-line package. Overcurrent protection, undervoltage lockout, and logic inputs for both latched and unlatched shutdown modes are also included.

#### Start-up/Preregulator Circuit

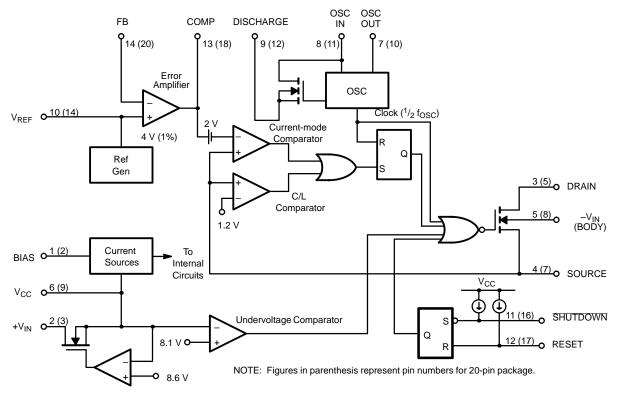

A unique start-up/preregulator circuit, which is shown in Figure 3, permits the Si9100 to operate over a wide input voltage range (10 to 70 V). The input voltage for the device is connected between the +V $_{\rm IN}$  (pin 2) and –V $_{\rm IN}$  (pin 5) terminals. The high-voltage depletion-mode (normally ON) MOSFET acts as a current source during start-up, charging the capacitance at the V $_{\rm CC}$  terminal (pin 6) directly from the input source. When V $_{\rm CC}$  exceeds the 8.1 V undervoltage threshold, the output switch is enabled to provide well-defined start-up characteristics. V $_{\rm CC}$  is then regulated to 8.6 V by the pre-regulator circuit. If an external voltage source greater than 8.6 V is fed to the V $_{\rm CC}$  terminal, the depletion-mode MOSFET is shut off to reduce power drain from the input power source.

#### Oscillator

The oscillator requires a single resistor to set its frequency. The requirements of flux reset in single-ended converters generally dictates a maximum duty cycle of 50%. With the oscillator frequency set at two times the desired switching frequency, a flip-flop divides the clock signal by two, and the logic disables the output during every other clock cycle.

FIGURE 3. Schematic Diagram of the Start-up Section of the Si9100

# VISHAY

# **Vishay Siliconix**

#### **MOSFET Switch**

The MOSFET switching transistor has typical  $~r_{DS(ON)}$  and  $V_{(BR)DSS}$  characteristics of 4  $\Omega$  and 180 V, respectively. Worst case specifications are 5  $\Omega$  and 150 V. The device is a lateral DMOS structure which has external connections for the DRAIN (pin 3) and SOURCE (pin 4). The body of the MOSFET is internally tied to the  $-V_{IN}$  terminal, which must be connected to the most negative input potential in the circuit.

#### **Error Amplifier**

The error amplifier permits compensation of control loops for stable regulator operation. The amplifier uses PMOS input transistors to provide high input impedance (2  $\mathrm{M}\Omega$  minimum), and is internally compensated for unity gain stability, with 1 MHz (typical) bandwidth and  $60^{\circ}$  phase margin.

#### **Protection**

In addition to the undervoltage lockout function already described, the Si9100 provides overcurrent protection and inputs for external logic control. With a sense resistor (typically 1 to 2  $\Omega$ ) connected from the MOSFET source to the  $-V_{IN}$  terminal, the voltage at pin 4 is proportional to the output current. When this voltage exceeds a 1.2 V reference the overcurrent comparator disables the output MOSFET. The shutdown delay is typically 100 ns (200 ns maximum).

Logic inputs SHUTDOWN (pin 11) and RESET (pin 12) permit the use of latched or unlatched shutdown modes. Internal current source pull-ups normally hold both logic pins high. If the SHUTDOWN pin is pulled low while the RESET is high, then the output switch will be disabled until the SHUTDOWN pin is again allowed to go high. This is the unlatched shutdown mode. If, however, the RESET pin is pulled low while the SHUTDOWN pin is also pulled low, then the converter will be latched off until RESET goes high again.

#### **FLYBACK CONVERTER OPERATION**

#### Start-Up

Applying input voltage to the circuit initiates charging of capacitor,  $C_1$ , through the filter inductor,  $L_1$ . The depletion-mode MOSFET, as described above, supplies current to capacitor  $C_5$  through the  $V_{CC}$  terminal of the IC. When  $V_{CC}$  reaches the undervoltage threshold (8.1 V), then transistor switching begins. The 4 V reference and the voltage divider ratio formed by  $R_5$  and  $R_6$  cause the feedback winding,  $N_{S3}$ , to be regulated to +10 V. After start-up is complete the feedback voltage trips the comparator to turn off the pre-regulator circuit, and the Si9100 derives its bias power from the feedback winding. The power saved by this bootstrap technique is equal to the product of the IC supply current times the difference between  $V_{\text{IN}}$  and  $V_{\text{FB}}$ :

Power Saved =  $(600 \mu A) (48 V - 10 V) = 23 mW$

While this is not a great deal of power, it does represent 2.3% of the output for a 1 W supply. Integrated Services Digital Network (ISDN) applications require such techniques for bias power minimization in order to meet emergency-mode limits for the power-down state.

#### **Flyback Operation**

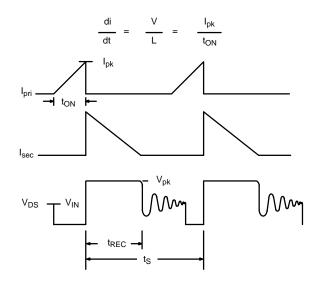

Flyback converter operation is illustrated by the basic waveforms shown in Figure 4. When the MOSFET switch is turned on, current will ramp up in the primary at a rate given by:

FIGURE 4. Flyback Converter Waveforms

Stored energy, given by  $^{1}/_{2}$  L<sub>P</sub>  $I_{pk}^{2}$ , is present in L<sub>2</sub> at the time the MOSFET is switched off. This energy is released to the secondary windings, N<sub>S1</sub> through N<sub>S3</sub>, during the off time, as shown by the total secondary current, I<sub>sec</sub>, in Figure 4.

This is the flyback principle in its simplest terms. A transformer is designed to transfer energy directly from the primary to the secondary, with as little stored energy as possible.

A flyback inductor receives energy during one interval of the switching cycle, then releases this stored energy at a later interval of the switching cycle.

During the time that the secondaries are conducting, shown as  $t_{REC}$ , the magnetic flux recovers, or "resets" to zero, and the MOSFET must block the sum of the reflected voltage from the secondary and the input voltage. This requires a worst case blocking voltage of:

$$V_{pk} = V_{IN} + \frac{N_P}{N_{S1}} (V_O + V_D)$$

= 70 +  $\frac{21}{8} (5.0 + 0.5) = 85 \text{ V}$

A leakage inductance spike appears at the leading edge of the  $V_{DS}$  waveform. The spike is less than the 150 V minimum  $V_{(BR)DSS}$ , and no snubber network is required. Since the flux is reset to zero before the end of each switching cycle, current flow through the secondary is discontinuous. Consequently, this circuit is called a discontinuous-conduction-mode (DCM) flyback converter.

#### **Regulator Control Loop**

The function of the regulator control loop is to maintain the output voltages constant as either the input line voltage or load current vary. These are termed "line regulation" and "load regulation", respectively.

A sense winding has been chosen to close the regulator loop and provide output isolation. Since the secondary windings are coupled on a common core, the volts/turn ratio is the same for  $N_{S1}$ ,  $N_{S2}$  and  $N_{S3}$ . The resulting secondary voltages will track each other quite closely. There is, however, some degradation in load regulation due to leakage (uncoupled) inductance between the  $^{1}/_{2}$  5-V output windings and the sense winding. This effect becomes progressively worse as the switching frequency is increased. The coupled inductor used here has been designed for good coupling between output and sense windings in order to maintain better than 5% regulation over the 0.2 W to 1 W load range. Design details for the coupled inductor are included in Appendix A.

To analyze the system closed loop response, begin by reflecting the filter capacitance and load resistance from each output winding to the feedback winding.

$$C_{eff} = C_5 + \left(\frac{N_{S1}}{N_{S3}}\right) \times \left(C_7 + C_9\right)$$

= 1  $\mu F + \left(\frac{8}{16}\right)^2 (100 \ \mu F + 20 \ \mu F) = 31 \ \mu F$

The effective load resistance,  $R_{\text{eff}}$ , can be found by assuming that the entire 1-W load is connected across the sense winding output:

$$R_{eff} = \frac{V_S^2}{P_O} = \frac{(10 \text{ V})^2}{1 \text{ W}} = 100 \Omega$$

The effective load impedance is determined at low frequency by the 100  $\Omega$  resistance and at high frequency by the capacitive reactance given by  $X_C=1/\omega C_{eff}.$  The control-to-output transfer function thus has a pole at:

$$f_p = \frac{1}{2\pi R_{eff}C_{eff}} = \frac{1}{2\pi (100)(31 \text{ x } 10^{-6)}} = 51 \text{ Hz}$$

To calculate the low frequency gain of the power stage, assume a 1 mV change in the error voltage,  $V_e$ , at the output of the error amplifier, and calculate the voltage change,  $\Delta V_S$ ,

which results at the feedback winding. Then combine the power stage gain with the error amplifier gain (including the voltage divider) to yield the total loop response. Assume for these calculations that the converter efficiency remains constant at 83.33%.

$$P_{IN} = \frac{P_0}{\eta} = \frac{1 \text{ W}}{0.8333} = 1.2 \text{ W}$$

The power input to the converter is the product of the stored inductive energy times the switching frequency.

$$P_{IN} = \frac{1}{2} L_p (I_{pk})^2 \cdot f_s$$

Rearranging to solve for Ipk gives:

$$I_{pk} = \sqrt{\frac{2 P_{IN}}{L_p x f_s}} = \sqrt{\frac{2(1.2) W}{(150 \mu H) 10^5 Hz}} = 0.4 A$$

Since the current sense resistor, R<sub>2</sub>, equals 1  $\Omega$ , a 1 mV change in the error voltage (at pin 13) will result in a 1 mA change in the peak inductor current, i.e.,  $\Delta I_{pk} = \Delta V_e$ . A 1 mA increase in  $I_{pk}$  causes  $P_{IN}$  to increase to:

$$P_{IN} = {}^{1}/{}_{2} L_{p} (I_{pk} + DI_{pk})^{2} S f_{s} =$$

${}^{1}/{}_{2} \cdot 150 S 10^{-6} (0.400 + 0.001)^{2} \cdot 10^{5} = 1.206 W$

Assuming efficiency remains constant,

$$P_O = (0.833) \cdot P_{IN} = 1.005 \text{ W}$$

This translates to an increase in the sense voltage to:

$$V_S = \sqrt{P_O \times R_{eff}} = \sqrt{(100 \times 1.005)} = 10.025 \text{ V}$$

The gain is given by:

$$\frac{\Delta V_{S}}{\Delta V_{e}} = \frac{10.025 \text{ V} - 10 \text{ V}}{1 \text{ mV}} = 25$$

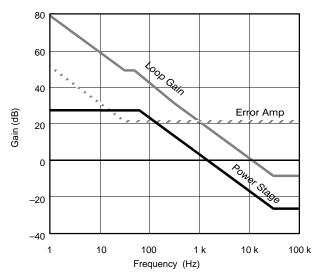

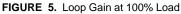

At full load the low frequency gain of the power stage is 25 (28 dB), with a single pole in the transfer function at 51 Hz. Performing a similar calculation at the 20% load condition yields a gain of 56 (35 dB) with a pole at 10 Hz. There will also be a zero in the transfer function at approximately 30 kHz due to capacitor ESR.

The solid line in Figure 5 represents the transfer function of the converter power stage at full load. The corresponding curve at a 20% load is shown in Figure 6. To complete the analysis of the control loop requires accounting for the resistive voltage divider and the error amplifier. The resistor  $R_6$  sets the dc bias condition, but does not enter into the small signal analysis.

FIGURE 6. Loop Gain at 20% Load

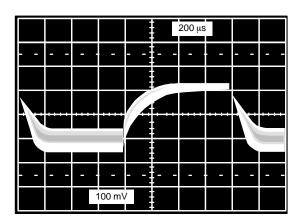

FIGURE 7. Step Load Response

At high frequencies the gain is  $R_4/R_5$ , with a zero occurring in the transfer function at

$$f_Z = \frac{1}{2\pi (240 \text{ k}\Omega) (0.022 \mu\text{F})} = 30 \text{ Hz}$$

The error amplifier response is shown in Figures 5 and 6 as dashed lines. The error amplifier response times the power stage gain gives the total loop gain, which is shown as the gray line for full load in Figure 5 and light load in Figure 6. Actual measurements of loop gain and phase yielded a loop bandwidth of 14 kHz with 68 degrees phase margin. Figure 7 shows the response of the +5-V output as the load is stepped between 20% and 100% of full load. Response time is under 200  $\mu s$  with no overshoot.

#### **ISDN APPLICATIONS**

Integrated Services Digital Network (ISDN) poses some unique problems to telecom systems design engineers. Standards proposed by the International Telephone and Telegraph Consultative Committee (CCITT) recommend that input power to ISDN terminal equipment (TE) meet the limits outlined in Table I<sup>1</sup>.

| TABLE 1. ISDN POWER REQUIREMENTS |                                 |                      |

|----------------------------------|---------------------------------|----------------------|

| Operating Mode                   | Maximum<br>Input Power<br>to TE | Efficiency<br>Target |

| Normal-active                    | 900 mW                          | 70%                  |

| Normal-power down                | 100 mW                          | 60%                  |

| Emergency-active                 | 400 mW                          | 70%                  |

| Emergency-power down             | 25 mW                           | 40%                  |

The 25-mW limit during emergency power-down mode operation may be especially troublesome<sup>2</sup>. In order to supply 10 mW to the TE for such functions as memory back-up, total converter losses must be less than 15 mW. Under such light load conditions the major power loss is in the PWM controller. Only controllers implemented in CMOS can presently be expected to meet this requirement.

Although the converter circuit of Figure 1 was not designed specifically for use in ISDN terminals, with some modifications it can be used in these applications. Since CMOS logic circuits consume power only during switching transitions, the first modification which is recommended is to decrease the switching frequency. The coupled inductor,  $L_2$ , can be operated at 40 to 50 kHz (change  $R_3$  from 150 k $\Omega$  to 390 k $\Omega$ ) without a redesign. Decreasing the frequency further requires a larger core size.

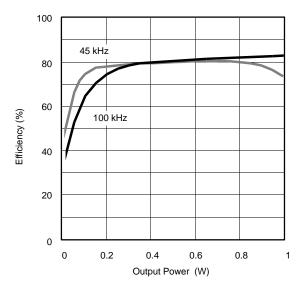

A second circuit modification which is recommended is to increase the resistances used in the voltage divider network ( $R_5$  and  $R_6$ ). The values used in the 1 W converter will dissipate (10)²/(18 k $\Omega$  + 12 k $\Omega$ ) = 3.33 mW. This loss is negligible for the 1 W converter, but it is nearly one fourth of the budgeted power loss for the ISDN supply during the emergency power-down state. Setting  $R_5$  = 51.1 k $\Omega$  and  $R_6$  = 34.0 k $\Omega$  reduces the voltage divider dissipation to 1.2 mW. With these two minor changes the flyback converter meets the efficiency specifications of Table I. Figure 8 illustrates the efficiency improvement at light load levels which results from the circuit changes outlined above.

#### **OTHER SI9100 APPLICATIONS CIRCUITS**

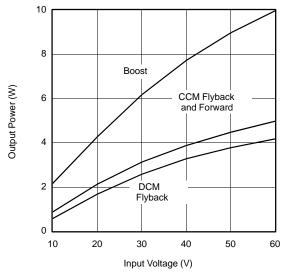

The Si9100 has been called a "One Watt High-Voltage Switchmode Regulator" in order to describe its most appropriate type of application--low power converters. The device is not, however, limited to 1 W designs. Figure 9 shows

FIGURE 8. Efficiency vs. Load Curves For The Flyback Converter

the maximum achievable output power as a function of minimum input voltage for several types of converters, two of which are discussed below.

#### **CCM Flyback Converter**

By redesigning the magnetics for continuous conduction, the flyback circuit of Figure 1 can be made to provide 3 W of output power. Operation in the continuous conduction mode (CCM) introduces a right-half-plane (RHP) zero into the control-to-output transfer function of the power stage. The RHP zero incurs a phase lag without the corresponding gain rolloff caused by left-half-plane poles, and lead compensation cannot be used. Instead, the gain must be rolled off to unity (0 dB) below the RHP zero frequency. The continuous-mode flyback will, therefore, have a slower dynamic response than the DCM flyback. Also, to maintain the same output ripple for the 3 W converter, it is necessary to increase the size of the output filter capacitors.

#### **Forward Converter**

Forward converters are not normally used for power supplies rated under 50 W, due to the additional cost of the output filter chokes. However, for 2- to 4-W converter applications requiring ultra-low ripple, the cost of the additional inductor may be warranted. One such application is low power instrumentation for avionics.

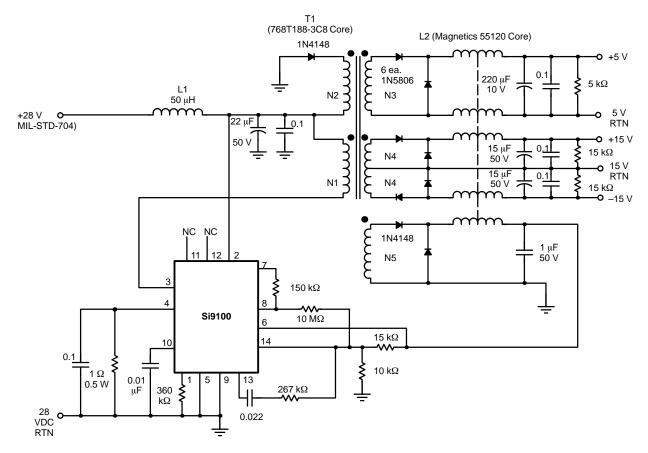

The forward converter of Figure 10 was designed to operate from 28-V aircraft power (MIL-STD-704D) to provide 2.5 W at 80% efficiency. A single core with multiple windings has been used to decrease cost and board space required for the output filter inductors. The input voltage range is 18 to 32  $\rm V_{DC}$ ; regulation is 5%; and the switching frequency is 100 kHz. Measured peak-to-peak voltage ripple was 8 mV for the +15-V output, 4 mV for the –15-V output, and 13 mV for the +5-V output, at maximum load.

FIGURE 9. Maximum Output Power vs. Minimum Input Voltage

FIGURE 10.2.5-W Forward Converter Using the Si9100

Toroidal cores were used for both the transformer and the coupled output inductor to achieve very low leakage inductance. The transformer winding data is as follows:

#### Core - Ferroxcube #768T188-3C8

Windings - N1 = 31 turns (AWG26)

N2 = 31 turns (AWG34)

N3 = 22 turns (AWG32)

N4 = 64 turns (AWG32)

N5 = 43 turns (AWG34)

The primary and clamp windings are placed on the core first, wound bifilar to minimize leakage inductance. The +5-V output is wound next, followed by the  $\pm\,15\text{-V}$  outputs wound bifilar. The 10-V winding was placed on the outside. Each winding is spread over the entire circumference of the toroidal core for optimum magnetic coupling.

Coupled inductors must have the same turns ratios as the transformer secondaries or high circulating currents result in very high output ripple. The coupled inductor,  $L_2$ , is a molypermalloy powder (MPP) toroid (Magnetics #55120) with three times the number of turns as each of the T1 secondaries. The inductor winding data is as follows:

- +5 V 66 turns (AWG30)

- +15 V 192 turns (AWG30)

- -15 V 192 turns (AWG34)

- +10 V 129 turns (AWG34)

It should be mentioned here that MIL-STD-461 EMI testing was not performed for this supply. To meet CE03 and CS01 limits, some input filter redesign is required. Although current-mode control exhibits excellent audio-susceptibility performance, it is still necessary to damp the input filter to reduce peaking of its output impedance at the resonant frequency (Reference 3 provides useful design information regarding these requirements).

#### References

- Rosenbaum, D. and Stolp, K. H., "The Feeding Conception of the ISDN Basic Access," IEEE Intelec Conference, Munich, FRG, Oct 14-17, 1985, pp. 505-512.

- Krautkramer, W. and Schickling, B., "Remote Power Feeding of ISDN Terminals at the Basic Access," IEEE Intelec Conference, Munich, FRG, Oct 14-17,1985, pp. 513-519.

- Middlebrook, R. D., "Input Filter Considerations in Design and Application of Switching Regulators," IEEE Industry Applications Society Annual Meeting, Oct. 11-14, 1976.

#### APPENDIX A: FLYBACK INDUCTOR DESIGN

#### **Inductance Calculation**

The first step is to calculate the maximum primary inductance for discontinuous conduction at maximum load. Input power to the coupled inductor is approximately:

$$P_{IN} = \frac{1 \text{ W}}{0.8} = 1.25 \text{ W} \tag{1}$$

Input power is also equal to the product of the stored energy in the magnetic field times the switching frequency:

$$P_{IN} = \frac{1}{2} L_P (I_{pk})^2 \cdot f_s \tag{2}$$

The minimum primary current slope occurs at the minimum input voltage condition.

$$\frac{di}{dt}\Big|_{MIN} = \frac{V_{IN(MIN)}}{L_{P(MAX)}}$$

If a maximum duty ratio of 0.45 is assumed, then the minimum current peak is given by:

$$\begin{split} &I_{pk} \leq \frac{di}{dt}\Big|_{MIN} \ x \ 0.45 \ T_S \\ &\text{or} \\ &I_{pk} \leq \frac{V_{IN(MIN)}}{L_{P(MAX)}} \ x \ 0.45 \ T_S \end{split} \tag{3}$$

Combining equations 2 and 3 gives:

$$\begin{split} & P_{\text{IN(MAX)}} = \frac{1}{2} L_{\text{P(MAX)}} \ I_{\text{pk(MIN)}}^2 x \ f_S \\ & = \frac{1}{2} L_{\text{P(MAX)}} \left( \frac{V_{\text{IN(MIN)}}}{L_{\text{P(MAX)}}} \right)^2 \left( 0.45 \ T_S \right)^2 f_S \\ & = \frac{1}{2} \ \frac{V_{\text{IN(MIN)}^2}}{L_{\text{P(MAX)}}} \ x \ \left( 0.45 \ T_S \right)^2 \ f_S \\ & \therefore \ L_{\text{P(MAX)}} = \frac{1}{2} \frac{V_{\text{IN(MIN)}^2}}{P_{\text{IN(MAX)}}} \ x \ \left( 0.45 \ T_S \right)^2 f_S \\ & = \frac{1}{2} \ \frac{(15)^2}{1.25} \ x \ \left( 0.45 \ T_S \right)^2 \ 10^5 = 182 \ \mu H \end{split}$$

To allow for component tolerances choose a nominal primary inductance of 150  $\mu H.$  Equation 2 then gives  $I_{pk}\approx 0.4$  A.

#### **Core Selection**

The area product method was used to determine the inductor core size. Refer to "Magnetic Core Selection for Transformers and Inductors" by McLyman, for more information on magnetics design methods (Marcel Dekker, Inc., 1982).

$$A_{p} = \left(\frac{2 E \times 10^{4}}{B_{m} \times K_{u} \times K_{j}}\right)^{1.14}$$

where:

$\begin{array}{ll} E &= \text{Core energy storage requirement} \\ B_m &= \text{Maximum flux density} \\ K_u &= \text{Window utilization factor} \\ K_i &= \text{Current density coefficient} \end{array}$

$$E = \bigcup L_P I_{pk}^2$$

Let  $B_m = 1500$  gauss = 0.15 tesla, and  $K_u = 0.10$

$$A_{P} = \left(\frac{2 \times \frac{1}{2} \times 150 \times 10^{-6} (0.4)^{2} \times 10^{-6}}{0.15 (0.10) (433)}\right)^{1.14}$$

$$= 0.0233 \text{ cm}^{4}$$

Since the empirical equation given above applies for the area product of simple one-winding inductors, multiply by 2 for a coupled inductor. All of the secondaries combined will handle the same energy as the primary, and can therefore be allotted equal portions of the window area. The area product requirement is thus:

$$A_P = 2 \cdot 0.0233 \text{ cm}^4 = 0.0466 \text{ cm}^4$$

The EP-13 core has an area product of 0.049 cm<sup>4</sup>, which meets this requirement. Also, this EP core can be tube-loaded for automatic insertion in high volume manufacturing applications, and is available from multiple sources (Siemens, TDK, and Amperex Ferroxcube).

#### Core A<sub>L</sub> Value Determination

The number of primary turns is found from:

$$L = \frac{N_P \Phi}{I_{nk}} = \frac{N_P B_m A_C}{I_{nk}}$$

Limiting the peak flux density to 0.15 Tesla gives:

$$\begin{split} N_P &= \frac{L_P I_{pk}}{B_M A_C} = \frac{(150 \times 10^{-6})(0.4) \times 10^4}{(0.15)(0.195 \text{ cm}^2)} \\ &= 20.5 \text{ turns} \simeq 21 \text{ turns} \end{split}$$

This gives the following value for A<sub>L</sub>:

$$A_L = \left(\frac{1000}{21}\right)^2 (150 \times 10^{-6}) = 340 \text{ mH per } 1000 \text{ turns}$$

#### **Secondary Turns Calculation**

The core flux is reset to zero during the off time for each switching cycle. To guarantee discontinuous conduction mode at the maximum load condition, it is necessary to limit the inductance of the secondary windings to some maximum value. Worst case conditions occur at the maximum switching frequency (110 kHz) and maximum  $A_L$  value (374 mH/1000 turns for 10 % tolerance). The voltage across  $N_{S1}$  during the diode conduction interval is  $V_O + V_D = 5.0 + 0.5 = 5.5$  V, and the negative current slope is

$$\frac{di}{dt} = \frac{I_{S1}}{d_{REC}} = \frac{V_O + V_D}{L_{S1}}$$

where  $l_{S1}$  is the peak current in the  $N_{S1}$  winding,  $t_{REC}$  is the conduction time of CR2, and  $L_{S1}$  is the inductance of  $N_{S1}.$  The rectifier conduction duty ratio is defined as:

$$d_r = \frac{t_{REC}}{T_S}$$

The load current is related to the peak secondary current and duty ratio by the equation:

$$I_{SI} = \frac{2 \times I_{O}}{d_{r}}$$

Combining these equations solves for the rectifier conduction duty ratio in terms of load current, inductance, and output voltage.

$$d_r = \sqrt{\frac{2 \times I_{O \times} L_{SI}}{(V_O + V_D) \times T_S}}$$

Setting the duty ratio < 0.45 gives:

$$d_r = \sqrt{\frac{2 \times 0.167 \times L_{S1}}{5.5 \times 9.09 \times 10^{-6}}} \le 0.45$$

Therefore,  $L_{S1}$  < 30.3  $\mu$ H. Since  $AL_{(MAX)}$  = 374 mH/1000 turns,

$$L_{S1} = \frac{N_{S1}}{5.5 \text{ V}}$$

Use  $N_{S1} = N_{S2} = 8$  turns:

$$N_{S3} = (10 \text{ V} + 0.7 \text{ V}) \frac{N_{S1}}{5.5 \text{ V}}$$

= 15.6 turns

$$\simeq$$

16 turns

#### Winding Order

The primary winding (1-2) is placed first over the bobbin using one strand of AWG31 magnet wire (21 turns). The highest current secondary (3-4) is wound over the primary using two strands of AWG31 (8 turns). The 10-V sense winding (7-8) is put down next, using one strand of AWG36 (16 turns). The -5-V output (5-6) is wound last using one strand of AWG31 wire (8 turns).

Document Number: 70584

#### **APPENDIX B: SI9100 FLYBACK CONVERTER PARTS LIST**

| U1             | Si9100                                                                       |

|----------------|------------------------------------------------------------------------------|

| L1             | Inductor, 100 $\mu H$ @ 75 mA dc, Vishay Dale ISC-1210 100 $\mu H$ $\pm10\%$ |

| L2             | Coupled Inductor, GFS Mfg. # 85-787-4* GFS Manufacturer                      |

| C1             | 20 $\mu\text{F}$ , 100 V, Aluminum Electrolytic, Vishay Sprague # 30D+TE1409 |

| C2, C3, C6, C8 | 0.1 μF ceramic, Vishay Vitramon VJ 1206Y104KXXAT                             |

| C4             | 0.022 μF ceramic, Vishay Vitramon VJ 1206Y223KXXAT                           |

| C7             | 100 μF, 10 V, tantalum, Vishay Sprague # 199D107X9010P                       |

| C9             | 20 μF, 10 V, tantalum, Vishay Sprague # 199D226X9010J                        |

| C5             | 1 μF, 50 V, WIMA MKS2                                                        |

| CR1            | 1N4148                                                                       |

| CR2, CR3       | 1N5819, Schottky rectifier                                                   |

| R1             | 390 kΩ, $^{1}/_{4}$ W Carbon                                                 |

| R2             | $1 \Omega$ , $\frac{1}{2}$ W Carbon                                          |

| R3             | 150 k $\Omega$ , $^{1}/_{4}$ W Carbon                                        |

| R4             | 240 k $\Omega$ , $^{1}/_{4}$ W Carbon                                        |

| R5             | 18 k $\Omega$ , $^{1}/_{4}$ W Carbon                                         |

| R6             | 12 k $\Omega$ , $^{1}/_{4}$ W Carbon                                         |

<sup>\*</sup> GFS Manufacturing Company, 21 Crosby Road, Dver, NH, USA 03820-1409